RISC-V 生态架构浅析

前言

RISC-V最近越来越多的出现在科技新闻中,大量的公司加入到RISC-V研究和生产中。在越来越多的RISC-V研究热下,毋容置疑的是RISC-V的时代即将到来。让我们在这浪潮翻滚起来前,一起掀开RISC-V的神秘面纱,提前了解一下RISC-V究竟是什么。

什么是RISC-V

RISC-V应该泛指RISC-V指令集及其衍生出来的一系列生态。而RISC-V指令集,类似于INTEL的X86 ,ARM指令集,是一个被CPU读取到内存后,指导计算机运行的指令集合。实现了该指令集的CPU,能执行指令集中规定的所有基本指令,使按该套指令集编译的程序能够无障碍运行,且具有同系列CPU可移植和兼容性。

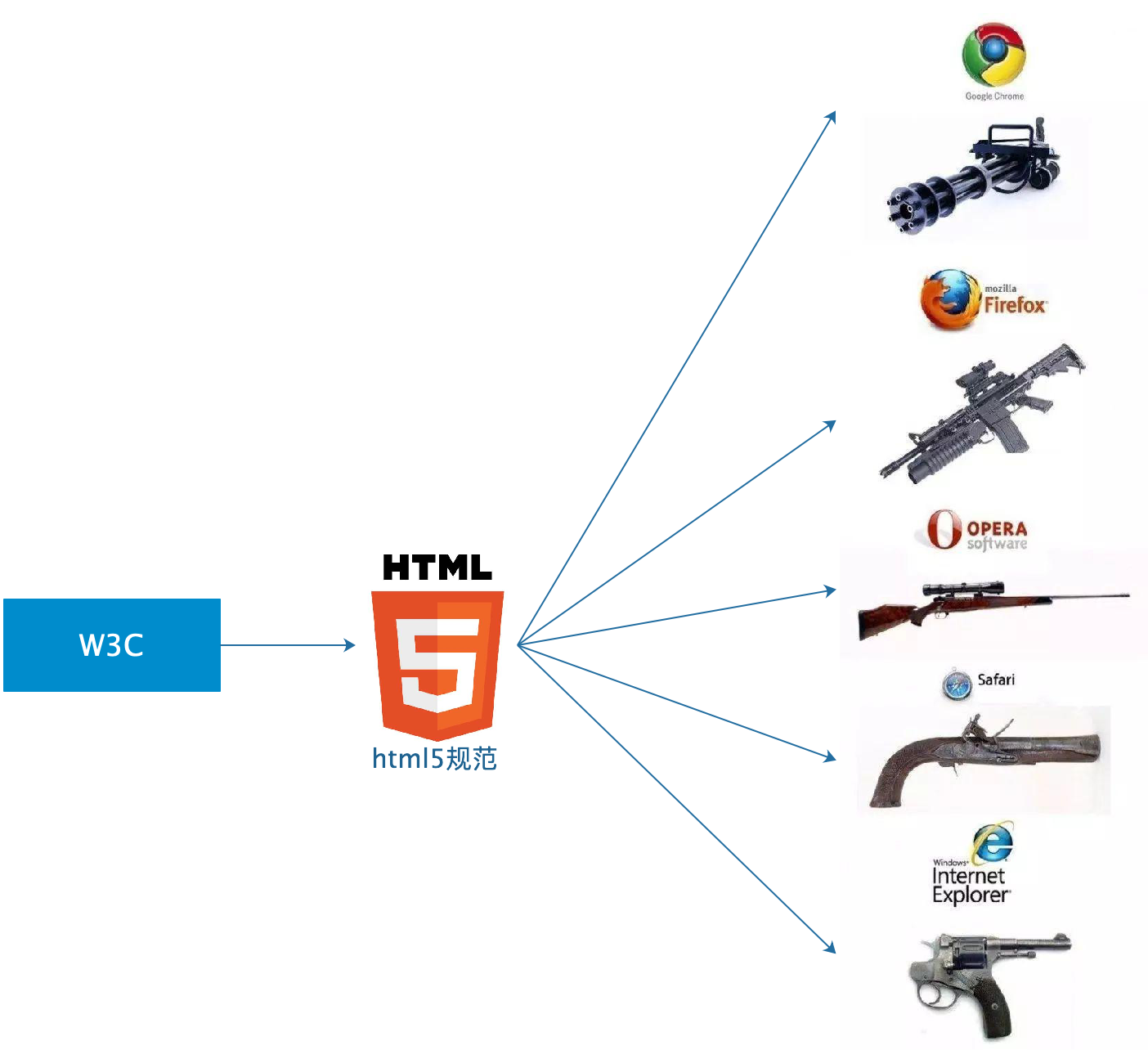

指令集有点类似于HTML规范,只是定义了基本的语法和规则。各个浏览器厂商依据该规范,自行投入研发能力实现出不同的产品,如下图所示。同一套HTML5规范,各个浏览器开发商实现的质量各有千秋,很显然让前端开发崩溃的IE已经如图所示自杀了,微软Edge已经转向了Chrome的怀抱。

![]()

在芯片领域,应用范围最广的指令集都是收费的(X86基本不对外授权,ARM费用相当不菲),你能想象HTML5标记语言需要花几百万上千万美元授权才能开发浏览器吗?这真的是难以想象!所以芯片设计领域迫切需要一个行业认可的,高品质的指令集,它应该是OPEN的,免费的,一个世界范围可以参考使用的芯片指令标准。

RISC-V指令集正式因为伯克利大学想开发一款CPU时,要么是一些老旧的架构,要么收费昂贵,芯片设计领域亟需一个开源的指令集。神说要有光,就有了光,神说要有空气,就有了空气,神说要有好的开源指令集,于是就有了RISC-V,没有好的轮子就造个轮子。RISC-V基金会就如W3C,RISC-V指令集就如HTML5,HTML5掀起了web领域的一场革命,RISC-V也将带来芯片领域的一场革命。

![]()

为什么不自己设计一套指令集?

目前应用领域最流行的两大指令集是X86和ARM,一个主宰服务器和PC,另一个主宰移动领域。X86被Intel,&AMD两家美国公司垄断; ARM指令集以前是英国的,现在已经被日本软银收购。而特朗普贸易战多动症发作的时候,这些指令集都被限制对华为授权或者销售。因为他们很大一部分都在美国霸权主义的控制范围之内。

![]()

很多人会问,RISC-V也是美国人发起的,话语权依然在美国人手里面。为啥中国不自己搞一套指令集,即便从RISC-V借鉴一下,搞个CRISC-6也可以。据说RISC-V第一版本指令集伯克利大学4个人从设计到发布只用了3个月。

这个就和HTML5标准是类似的,全球的浏览器应该基于一套免费的,开放的W3C制定的标准,而不是另起炉灶各自开发。否则你将不能得到大量开源社区的支持,如Linux社区,JDK相关支持,你将在全球首肯的生态圈外,最终要死不活。就像IE的自定义HTML标记,除非有个微软这样的好爸爸才有人基于你进行开发。然而即使IE有个好爸爸,最后还是挂了,因为对W3C的兼容性太差,让开发者痛苦的技术一定会被抛弃!故而处理器架构必须是全球范围的一个通用架构,必须获得生态支持,指令集不难,难得是成为事实标准并被全球采纳,被顶级工程师和开源社区主动提供适配支持。

世界需要技术标准,从IEEE,W3C到5G。技术标准可以让世界沟通更加流畅,节省更多的开发成本!

BSD协议,在RISC-V指令集基于这一开源领域非常自由的开源协议发布时,我们暂且相信这一指令集如该协议声明的那样开放。在RISC-V发展进程中,去拥抱它,发展它,合作构建一套自主可控且全球公认的指令集生态。如果有一天被限制了,基于BSD协议去兼容它。毕竟按常理国外一开源,国内就自主这个套路还是可以继续使用的。何况RISC-V本身只是一套指令集标准和规范。

缘起

该项目2010年始于加州大学柏克莱分校,但许多贡献者是该大学以外的志愿者和行业工作者。

在2010年,伯克利研究团队要设计一款CPU,然而,英特尔对X86的授权卡的很严,ARM的指令集授权很贵,MIPS、SPARC、Open Power也都需要各自的公司授权。在选择很有限的情况下,伯克利的研究团队决定从零开始设计一套全新的指令集。而被很多媒体大肆宣扬也让人振奋的是,伯克利的研究团队4名成员仅用了3个月就完成了RISC-V的指令集开发,并公开发布了第一版指令集。正如行业内常说的,设计一套指令集并非黑科技,用这套指令集去实现CPU 才是真正具有含金量的工作。该指令集的第一个版本只包含了不到50条指令,可以用于实现一个具备定点运算和特权模式等基本功能的处理器。目前,伯克利研究团队已经完成了基于RISC-V指令集的顺序执行的64位处理器核心(代号为Rocket),并前后基于45nm与28nm工艺进行了12次流片。Rocket芯片主频1GHz,与ARM Cortex-A5相比,实测性能较之高10%,面积效率高49%,单位频率动态功耗仅为Cortex-A5的43%。在嵌入式领域,Rocket已经可以和ARM争市场了。

RISC-V指令集具有性能优越,彻底免费开放两大特征。RSIC-V的设计目标是能够满足从微控制器到超级计算机等各种复杂程度的处理器需求,支持从FPGA、ASIC乃至未来器件等多种实现方式,同时能够高效地实现各种微结构,支持大量定制与加速功能,并与现有软件及编程语言可良好适配。

PS:伯克利大学世界大学排名世界第4、世界大学学术排名世界第5。

发展

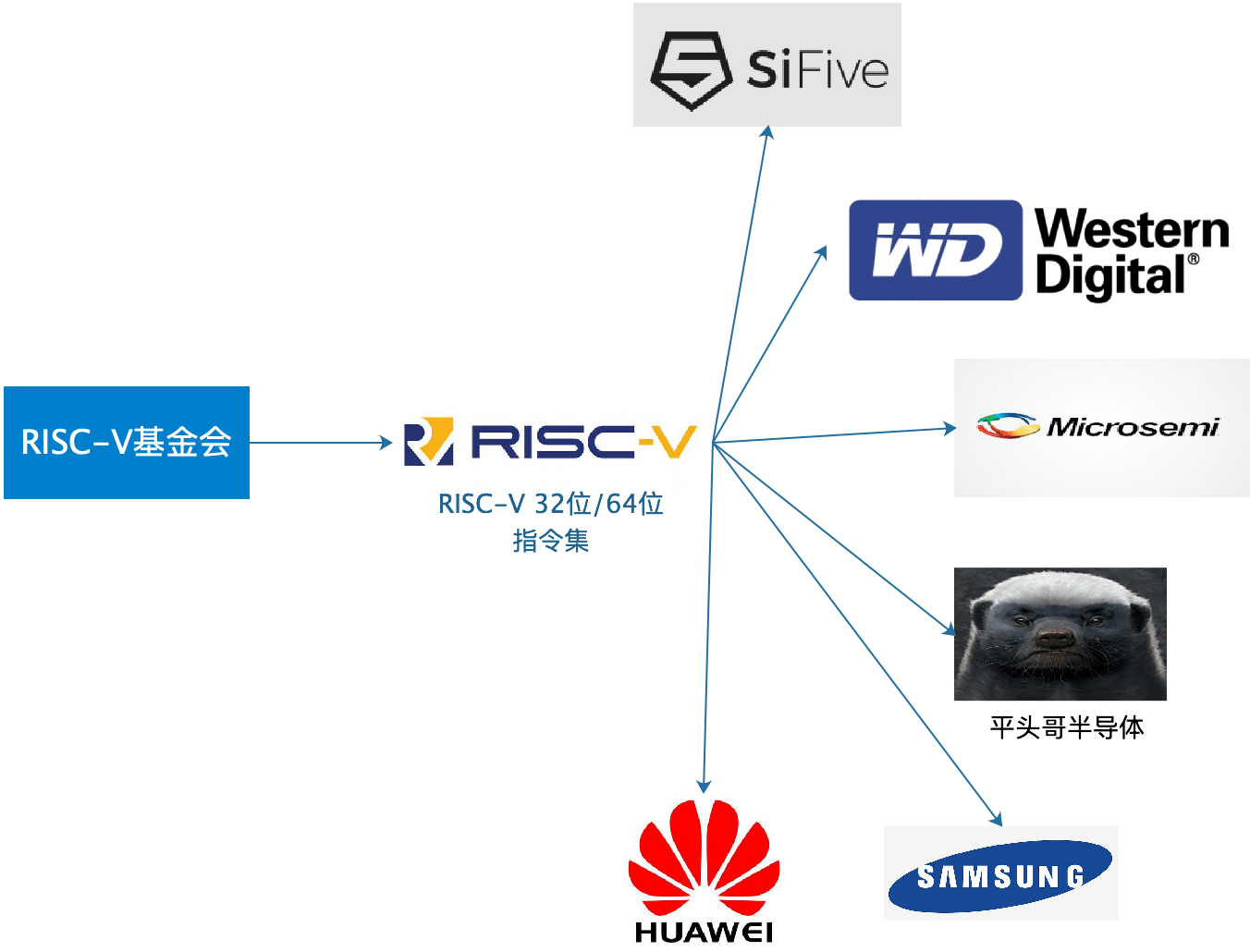

RISC-V产业生态正进入快速发展期。加州大学伯克利分校在2015年成立非盈利组织RISC-V基金会,该基金会旨在聚合全球创新力量共同构建开放、合作的软硬件社区,打造RISC-V生态系统。三年多来,谷歌、高通、IBM、英伟达、NXP、西部数据、Microsemi、中科院计算所、麻省理工学院、华盛顿大学、英国宇航系统公司等200多个企业和研究机构先后加入了RISC-V基金会。

![]()

RISC-V大事件

-

全球第一大硬盘产商西部数据(Western Digital)将以每年10亿到20亿颗的预期来推动RISC-V,逐步完成全线产品迁移到RISC-V定制架构;

-

MicroSemi提供基于Risc-V+Linux+CNN加速器的AI解决方案;

-

印度政府则大力资助基于RISC-V的处理器项目,使RISC-V成为了印度的事实国家指令集;

-

RISC-V基金会的会员已经增加到150多个,大学、科研院所和企业大量使用或评估基于RISC-V的应用,参与度之高,覆盖面之广,盛况空前;指令集架构的生态链正在成长和完善,工具链、RTOS/Linux操作系统的移植等工作都取得关键突破;

-

2018年11月,RISC-V基金会宣布了与Linux基金会的联合合作。作为合作的一部分,Linux基金会还将为RISC-V生态系统提供大量资源,如培训项目、基础设施工具、社区推广、市场营销和法律专业知识;

-

2019年6月,Debian 移植 RISC-V 64 架构已完成 90%,LLVM 成阻碍,不过开发者预计今年将会完成对 LLVM for RISC-V 64 的支持。

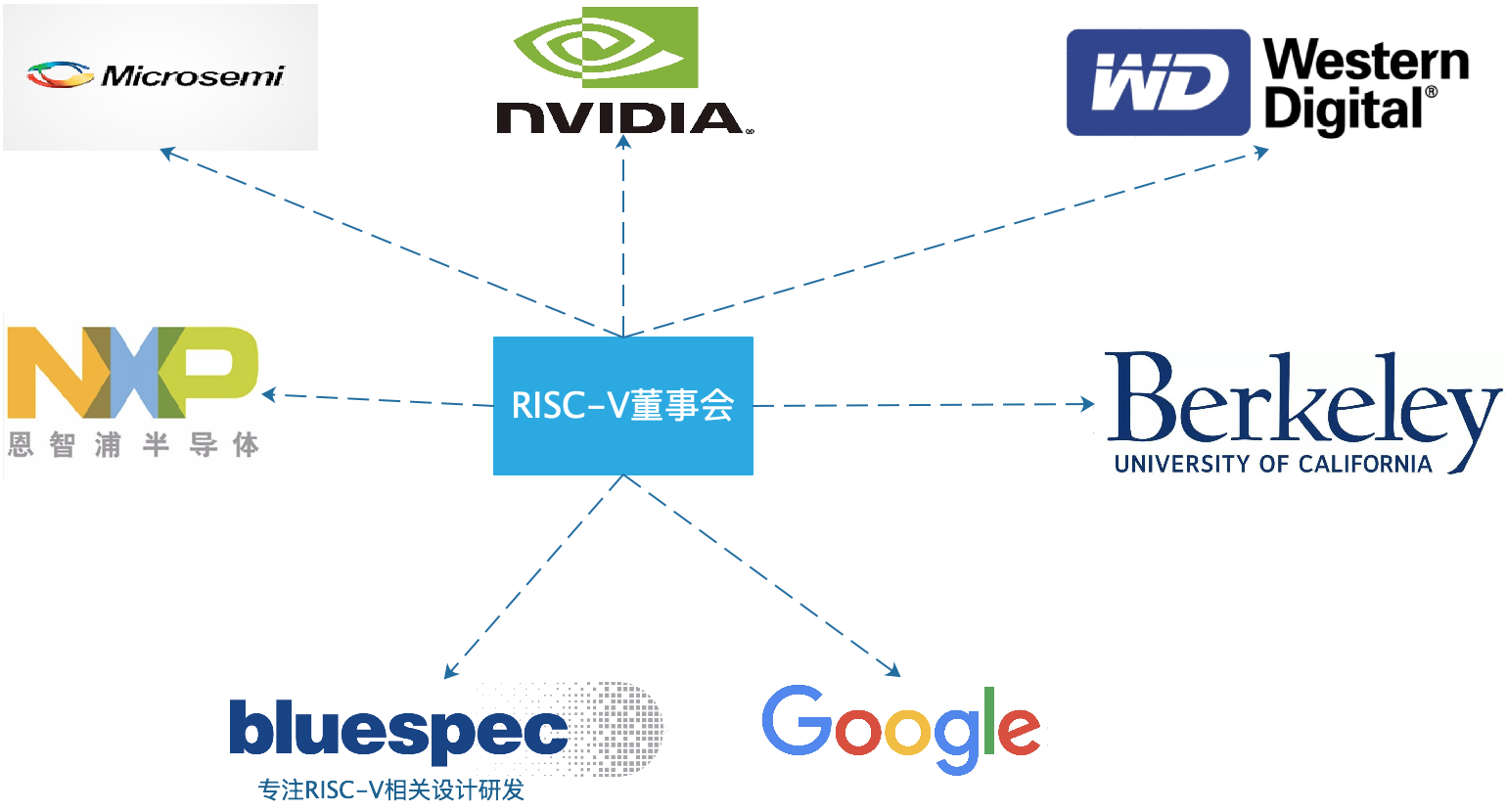

RISC-V 基金会

在RISC-V诞生5年后,2015年RISC-V基金会成立。有超过275个成员致力于建立第一个开放的,合作的软硬件创新社区。RISC-V ISA诞生于学术界和研究界(加州伯克利分校EECS系的计算机科学部),为未来50年的计算相关的设计与创新铺平了道路。

RISC-V基金会是一个由其成员控制的非营利性公司,指导RISC-V未来的发展,并推动RISC-V ISA的被更大范围的采用。RISC-V基金会的成员可以访问和参与RISC-V ISA规范和相关的HW/SW生态系统的开发。该基金会有一个董事会包括七个代表,分别来自Bluespec公司、谷歌、Microsemi、Nvidia、NXP、加州伯克利大学、和西部数据。

![]()

每年RISC-V基金会都会举办全球活动,将不断增长的生态系统整合在一起,讨论当前和未来的RISC-V项目和实现,以及共同推动未来的指令集体系结构(ISA)的演进。活动会议的特色是主要的技术公司和研究机构讨论:RISC-V体系结构、商业和开源实施、软件和硅半导体、向量和安全、应用程序和加速器、模拟基础设施等。访问事件处理页面了解更多信息。

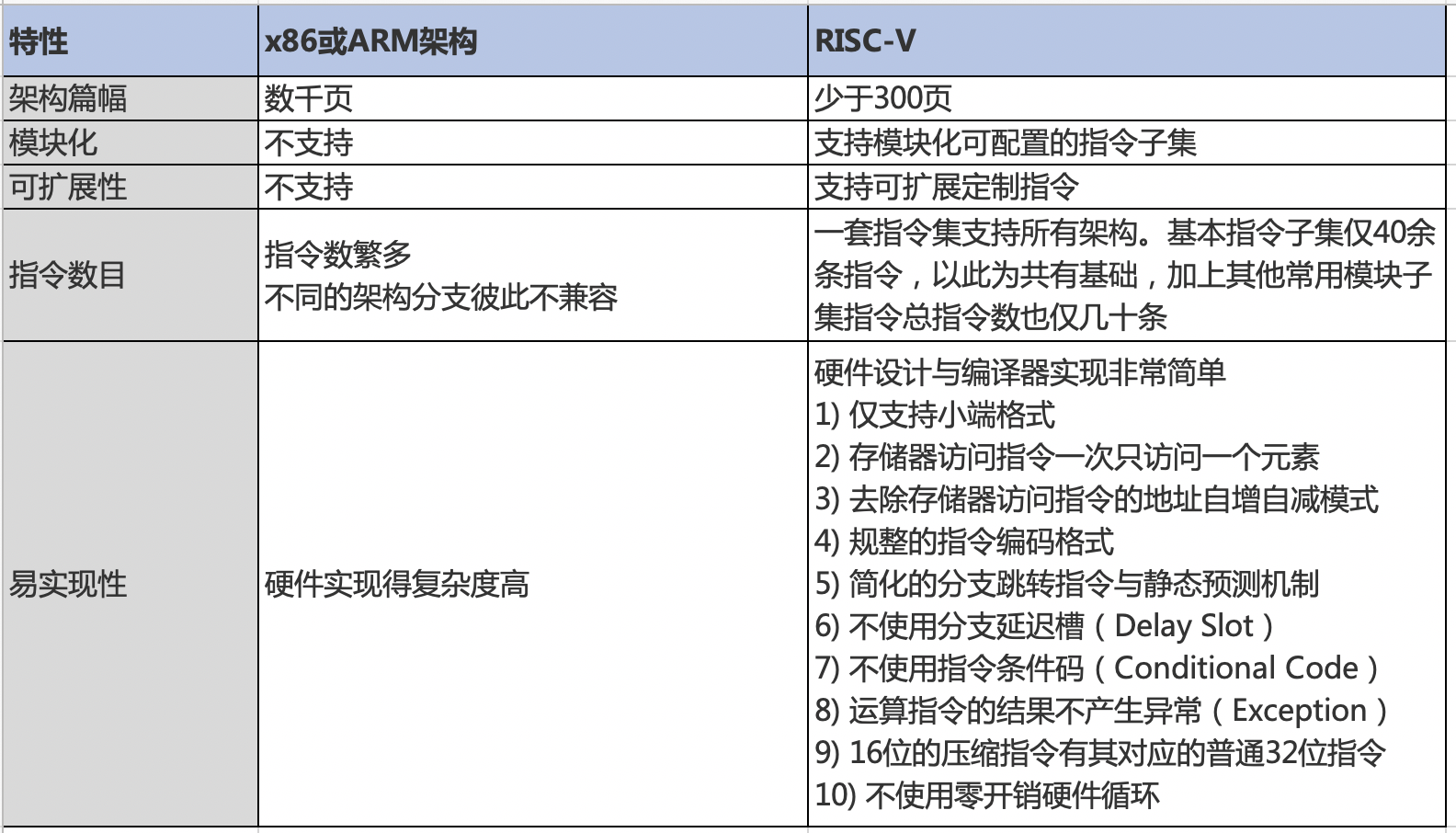

RISC-V 指令特点

1 设计哲学-简单就是美

大道至简,在IC设计的实际工作中,最简洁的设计往往是最可靠的,在大多数的项目实践中一次次的得到检验。

IC设计的工作性质非常特殊,其最终的产出是芯片,而一款芯片的设计和制造周期均很长,无法像软件代码那样轻易的升级和打补丁,每一次芯片的改版到交付都需要几个月的周期。不仅如此,芯片的一次制造成本费用高昂,从几十万美金到百千万美金不等。这些特性都决定了IC设计的试错成本极为高昂,因此能够有效的降低错误的发生就显得非常的重要。

1.1 无病一身轻——架构的篇幅

后发优势,RISC-V设计汲取X86和ARM架构中的经验,前人踩过的坑不用再犯,同时无需向下兼容老旧的设计和已经过时的指令。想想去看一本架构文档,里面一大半的篇幅都在讲过时的指令和设计,是不是感觉宝贵的时间都被浪费了。

在处理器领域,目前主流的架构为x86与ARM架构。经过几十年的发展,现代的x86与ARM架构的架构文档长达几百数千页。打印出来能有半个桌子高,可真是“著作等身”。之所以现代x86与ARM架构的文档长达数千页,且版本众多,一个主要的原因是因为其架构的发展的过程也伴随了现代处理器架构技术的不断发展成熟。并且作为商用的架构,为了能够保持架构的向后兼容性,其不得不保留许多过时的定义,或者在定义新的架构部分时为了能够将就已经存在的技术部分而显得非常的别扭。久而久之就变得极为冗长。

而现在才推出的RISC-V架构,则具备了后发优势,由于计算机体系结构经过多年的发展已经成为比较成熟的技术,多年来在不断成熟的过程中暴露的问题都已经被研究透彻,因此新的RISC-V架构能够加以规避,并且没有背负向后兼容的历史包袱,可以说是无病一身轻。

目前的“RISC-V架构文档”分为“指令集文档”(riscv-spec-v2.2.pdf)和“特权架构文档”(riscv-privileged-v1.10.pdf)。“指令集文档”的篇幅为145页,而“特权架构文档”的篇幅也仅为91页。熟悉体系结构的工程师仅需一至两天便可将其通读,虽然“RISC-V的架构文档”还在不断地丰富,但是相比“x86的架构文档”与“ARM的架构文档”,RISC-V的篇幅可以说是极其短小精悍。

1.2 能屈能伸——模块化的指令集

RISC-V架构相比其他成熟的商业架构的最大一个不同还在于它是一个模块化的架构。因此,RISC-V架构不仅短小精悍,而且其不同的部分还能以模块化的方式组织在一起,从而试图通过一套统一的架构满足各种不同的应用。

这种模块化是x86与ARM架构所不具备的。以ARM的架构为例,ARM的架构分为A、R和M三个系列,分别针对于Application(应用操作系统)、Real-Time(实时)和Embedded(嵌入式)三个领域,彼此之间并不兼容。

但是模块化的RISC-V架构能够使得用户能够灵活选择不同的模块组合,以满足不同的应用场景,可以说是“老少咸宜”。譬如针对于小面积低功耗嵌入式场景,用户可以选择RV32IC组合的指令集,仅使用Machine Mode(机器模式);而高性能应用操作系统场景则可以选择譬如RV32IMFDC的指令集,使用Machine Mode(机器模式)与User Mode(用户模式)两种模式。而他们共同的部分则可以相互兼容。

1.3 浓缩的都是精华——指令的数量

短小精悍的架构以及模块化的哲学,使得RISC-V架构的指令数目非常的简洁。基本的RISC-V指令数目仅有40多条,加上其他的模块化扩展指令总共几十条指令。

2. RISC-V指令集简介

2.1 模块化的指令子集

RISC-V的指令集使用模块化的方式进行组织,每一个模块使用一个英文字母来表示。RISC-V最基本也是唯一强制要求实现的指令集部分是由I字母表示的基本整数指令子集,使用该整数指令子集,便能够实现完整的软件编译器。其他的指令子集部分均为可选的模块,具有代表性的模块包括M/A/F/D/C,如表1所示。

2.2 规整的指令编码

在流水线中能够尽早尽快的读取通用寄存器组,往往是处理器流水线设计的期望之一,这样可以提高处理器性能和优化时序。这个看似简单的道理在很多现存的商用RISC架构中都难以实现,因为经过多年反复修改不断添加新指令后,其指令编码中的寄存器索引位置变得非常的凌乱,给译码器造成了负担。

得益于后发优势和总结了多年来处理器发展的教训,RISC-V的指令集编码非常的规整,指令所需的通用寄存器的索引(Index)都被放在固定的位置,如图2所示。因此指令译码器(Instruction Decoder)可以非常便捷的译码出寄存器索引然后读取通用寄存器组(Register File,Regfile)。

2.3 优雅的压缩指令子集

基本的RISC-V基本整数指令子集(字母I表示 )规定的指令长度均为等长的32位,这种等长指令定义使得仅支持整数指令子集的基本RISC-V CPU非常容易设计。但是等长的32位编码指令也会造成代码体积(Code Size)相对较大的问题。

为了满足某些对于代码体积要求较高的场景(譬如嵌入式领域),RISC-V定义了一种可选的压缩(Compressed)指令子集,由字母C表示,也可以由RVC表示。RISC-V具有后发优势,从一开始便规划了压缩指令,预留了足够的编码空间,16位长指令与普通的32位长指令可以无缝自由地交织在一起,处理器也没有定义额外的状态。

2.4 特权模式

RISC-V架构定义了三种工作模式,又称特权模式(Privileged Mode):

- Machine Mode:机器模式,简称M Mode。

- Supervisor Mode:监督模式,简称S Mode。

- User Mode:用户模式,简称U Mode。

RISC-V架构定义M Mode为必选模式,另外两种为可选模式。通过不同的模式组合可以实现不同的系统。

2.5 自定制指令扩展

除了上述阐述的模块化指令子集的可扩展、可选择,RISC-V架构还有一个非常重要的特性,那就是支持第三方的扩展。用户可以扩展自己的指令子集,RISC-V预留了大量的指令编码空间用于用户的自定义扩展,同时,还定义了四条Custom指令可供用户直接使用,每条Custom指令都有几个比特位的子编码空间预留,因此,用户可以直接使用四条Custom指令扩展出几十条自定义的指令。

2.6 其它特点

可配置的通用寄存器组;

简洁的存储器访问指令;

高效的分支跳转指令;

简洁的子程序调用;

无条件码执行;

无分支延迟槽;

简洁的运算指令;

3. 总结与比较

![]()

SIFIVE公司及开源

SIFIVE公司是RISC-V指令集的行业先驱。2015年,伯克利研究团队又往前推进了一步,成立了SiFive初创公司,加速RISC-V的商业化进程。SiFive公司的定位和基于Linux开源社区的RedHat公司、基于Spark开源社区的Databricks公司一样,为用户提供高性能的处理器IP核以及集成了外围部件IP的SoC芯片。

SIFIVE目前的产品类似于浏览器领域的开源产品chromium,当然区别在于chromuim相对开放,而SIFIVE在商业用途还是需要相关专利授权才可使用。目前已推出32位E2(低端)、E3(中端)、E7(高端)系列,和64位S2、S5、S7系列, 64位Linux兼容版U2,U7处理器。并着手于简化芯片设计领域的技术鸿沟,提供云端的模块化设计和验证程序。

SIFIVE目前也是RISC-V领域产品系列最全,技术相对领先的公司。其它芯片设计公司或多或少与其有合作和技术参考。2018年SIFIVE推出了全球第一款运行 Linux的HIFIVE开发板,核心芯片为 1.5GHz U540 SoC,采用台积电 28nm HPC 工艺制造的64位处理器,配备 8GB DDR4(ECC)、一个千兆以太网(GbE)端口、一个 microSD 插槽、FMC连接器。

![]()

SIFIVE中国:基于2019年5月,美国政府限制ARM公司向华为提供新的技术授权,同时也限制SIFIVE向华为提供芯片IP授权。SIFIVE在中国成立完全独立的子公司,SIFIVE中国完全独立运营,而非SIFIVE的子公司,以此来规避政治风波造成的技术性中断。

美国商务部前助理部长Kevin Wolf说,已公开发表、供任何人取用的科技,不被美国“出口管理条例”监管,也不受实体清单限制。RISC-V属于公开类别,是华为的潜在芯片替代方案。

SiFive的CEO Naveed Sherwani指出,“因为我们一直认为中国有权利需要一个非常独立的半导体行业。中国行业需要这样独立的企业,所以我们非常赞同这样的理念。如果您要在这个地方帮助中国,首先要是中国的企业”。当然SIFIVE的最终目的还是促进RISC-V生态环境的发展和壮大,最终成为比肩甚至超越X86和ARM的新一代计算指令集。

国内发展现状

政策扶持

国家大力推广,上海成为国内第一个将RISC-V列入政府扶持对象的城市,并发布了《上海市经济信息化委关于开展2018年度第二批上海市软件和集成电路产业发展专项资金项目申报工作的通知》。对RISC-V相关芯片设计企业提供政策资金帮助,鼓励基于RISC-V自主处理器的研发及产业化。

中国开放指令生态(RISC-V)联盟

2018年11月,中国开放指令生态(RISC-V)联盟(下简称“RISC-V中国联盟”)于8日在浙江乌镇召开的世界互联网大会上宣布成立。联盟理事长由中国工程院院士、中科院计算所研究员倪光南担任。图灵奖得主、美国加州大学伯克利分校教授David Patterson在成立仪式上发布了由中科院计算所翻译的中文版《RISC-V手册》。

RISC-V中国联盟旨在以RISC-V指令集为抓手,联合学术及产业界推动开源开放指令芯片及生态的健康发展。因此,联盟制定了一个“三步走”计划,希望用10年左右的时间,到2030年逐步完成开源芯片生态的建立。据了解,RISC-V中国联盟发起单位包括中科院计算所、北京大学、清华大学、阿里—中天微、百度、中芯国际等近20家研究机构和企业,目前已有一批企业构建了开源芯片关键技术。

“RISC-V指令集有望像开源软件生态中的Linux那样,成为计算机芯片与系统创新的基石。” RISC-V中国联盟秘书长、中科院计算所研究员包云岗对《中国科学报》记者说,但只有RISC-V指令集还远远不够,还需要开发基于RISC-V的开源工具链、开源IP、开源SoC等才能形成开源芯片生态,这需要更多支持开源芯片的力量参与和贡献。

黄山一号芯片

2017年,华米科技成立了人工智能实验室,并启动了他们的人工智能智能可穿戴芯片研究项目,投身 RISC-V 芯片研发,并最终在 2018 年 9 月推出了第一款芯片“黄山一号”。据介绍,这款采用RISC-V架构设计的芯片是是全球首款集成AI神经网络模块的处理器,能本地化处理AI任务,对心率、心电、心律失常等进行实时监测与分析。2019年6月“黄山一号”已流片量产,主要用于华米穿戴智能设备AMAZFIT的主控芯片,处理器频率240MHz,55nm工艺,目前应该是和SIFIVE合作采用了SIFIVE公司的部分芯片IP。

![]()

![]()

其它厂家机构

平头哥半导体(前杭州中天微):宣布正式推出支持RISC-V第三代指令系统架构处理器CK902,并建立战略合作关系推广RISC-V在国内的商业化落地。截至2018年9月,中天微基于C-SKY CPU IP核的SoC芯片累计出货量已经突破8亿颗。CK902为32位低功耗,是全球首款支持物联网安全的RISC-V处理器。

阿里平头哥首颗芯片玄铁910出炉,现场启动普惠芯片计划(2.5GHZ, 最高16核,开始暴走出击了??) http://baijiahao.baidu.com/s?id=1640007943128436792&wfr=spider&for=pc

** 松果电子(小米) ** 和中天微合作,以中天微RISC-V CPU处理器为基础平台,松果电子提供极具市场竞争力的SoC智能硬件产品,共同促进和加速RISC-V在国内的商业化进程。松果电子考量了中天微在现有嵌入式CPU研发技术、持续研发投入的经济的双实力,经过大规模量产验证的中天微CPU内核架构配合成熟稳定的开发工具链,在以此最大限度避免使用RISC-V时带来的技术和量产的不确定性。

** 上海乐鑫信息科技 ** 成立于2008年,致力于前沿低功耗WiFi+蓝牙双模物联网解决方案的研发。目前在研基于RISC-V指令集架构的ESP32-Marlin物联网芯片。

** 北京君正 ** 北京君正集成电路股份有限公司成立于2005年,目前已发展成为一家国内外领先的嵌入式CPU芯片及解决方案提供商。CPU研发队伍已展开对基于RISC-V指令集的CPU核的研发。

** 芯来科技 **: 创立于2018年,是一家具有代表性的RISC-V处理器内核IP和解决方案公司,并创造了我国第一颗开源RISC-V处理器项目蜂鸟E203。2019年1月芯来科技完成了千万级人民币的天使轮融资。

有数据显示,中国有300家以上公司在关注RISC-V或以RISC-V指令集进行开发,除了以上所列举的企业,采用RISC-V架构推出产品的还包括芯原、汇顶、核芯互联、飞利信等。

印度发展情况

从国家政策层面对于RISC-V进行支持,我国并非第一家。2017年,印度政府表示将大力资助基于RISC-V的处理器项目,使RISC-V成为了印度的事实国家指令集。

2011年印度实施处理器战略计划,在全国范围资助2-3个研制处理器的项目。印度理工学院马德拉斯分校的两位教授在该计划支持下启动了SHAKTI处理器项目,研制与IBM PowerPC兼容的处理器,为获得合法授权,SHAKTI项目组与IBM开展了合作谈判,但未能达成一致。此时恰好遇上RISC-V在2013年流片成功,于是SHAKTI项目组放弃PowerPC拥抱RISC-V,项目目标也临时调整为研制6款基于RISC-V指令集的开源处理器核。这个临时的调整不仅未受到指责,反而得到了印度政府更大力度的支持。另外,2016年1月,曾长期开展超级计算机研究的先进计算发展中心获得印度电子信息技术部4500万美元的资助,目标是研制一款基于RISC-V指令集的2GHz四核处理器。还有,在印度政府支持的另一个关于神经形态加速器项目中,也将RISC-V作为计算主核心。随着印度政府资助的处理器相关项目都开始向RISC-V靠拢,RISC-V成为了印度的事实国家指令集。

印度理工学院(IIT)Madras 为其开源Shakti处理器发布了SDK。Shakti基于开源RISC-V指令集架构,由印度电子和信息技术部资助。根据IIT的说法,开发板也将很快发布。IIT Madras的RISE集团于2016年开始致力于Shakti项目,并计划针对不同的市场发布六个系列的处理器。该集团表示,他们的处理器在面积、性能和功耗方面具有竞争力。Shakti处理器首批就规划了多达6个不同系列,各自针对不同的市场,号称在核心面积、性能、功耗方面相比当前商用处理器都很有竞争力。目前在研,低端产品有成品,中高端还在开发设计阶段。

E系列:3级顺序流水线,针对IoT物联网设备、机器人平台、电机控制等嵌入式领域。

C系列:32位5级顺序流水线,微控制器档次,核心频率200MHz-1GHz,适合中等负载,功耗极低,并可选支持内存保护。

I系列:64位乱序流水线,核心频率1.5-2.5GHz,支持多线程,面向移动、存储、网络应用,也是主打嵌入式。

M系列:面阿宁主流消费级市场,最多八核心。

S系列:针对工作站和服务器,I系列的增强版,也支持多线程。

H系列:用于高性能计算,单线程性能突出,可选四级缓存,支持Gen-Z Fabric互连总线、存储级内存。

![]()

RISC-V 可应用的领域

RISC-V可应用于FPGA,嵌入式,ADC/DAC 转换器,DSP 及服务器CPU等领域。

![]()

作为Java应用开发程序员,我们理想的状态应该全技术栈免费开源:

RISC-V 64位处理器 + Linux + MySQL + Docker + OPENJDK。

![]()

面临的问题

无论是Linux还是其它开源社区,还处于相向适配阶段,安全稳定运行还有待验证。

开发工具,验证工具还不够成熟。

生态不够完整,产业链主要是外围配件等中低端产品。

在高端主控和高性能服务器CPU相关,还没有应用范围广的成品。

各个厂家可自行设计实现自己的硬件,不排除如Android一样出现设备多样性,碎片化,测试人员面前一堆手机的场景复现。

友情链接

MoliCode自定义模板代码生成工具,如果有需要的可以参看一下,谢谢支持: https://www.oschina.net/news/108402/molicode-2-0-released

参考文献

risc-v基金会 https://riscv.org/

物联网给了RISC-V绝佳机会 http://www.elecfans.com/emb/dsp/20190515934806.html

RISC-V,才是未来的科技之芯 https://baijiahao.baidu.com/s?id=1634400236103047992&wfr=spider&for=pc

把RISC-V讲明白了 http://m.elecfans.com/article/653167.html

美国RISC-V厂商已不能向华为出售IP http://news.hqew.com/info-346602

中国开放指令生态(RISC-V)联盟 http://crva.ict.ac.cn/

RISC-V精简到何种程度? https://blog.csdn.net/zoomdy/article/details/79343941

大道至简——RISC-V架构之魂(上) https://blog.csdn.net/zoomdy/article/details/79580529

大道至简——RISC-V架构之魂(中) https://blog.csdn.net/zoomdy/article/details/79580772

大道至简——RISC-V架构之魂(下)https://blog.csdn.net/zoomdy/article/details/79580949

RISC-V学习整理 https://blog.csdn.net/csbei19891218/article/details/87880578

解读两大精简指令集:RISC-V和MIPS https://blog.csdn.net/qq_41394155/article/details/88595775

RISC-V的软件开发 https://blog.csdn.net/tomsoft/article/details/80915348

【一种全新的指令集架构RISC-V】 https://blog.csdn.net/p340589344/article/details/82290920

大量的RISC-V文章(可下载)https://blog.csdn.net/zzwu/article/details/54798818

芯片春秋: 开源架构RISC-V前世今生 https://blog.csdn.net/BtB5e6Nsu1g511Eg5XEg/article/details/80267054

第七章RISC-V的取指令 https://blog.csdn.net/qiaobt/article/details/83141066

什么是RISC-V https://zhuanlan.zhihu.com/p/49176102

RISC-V登场,Intel和ARM会怕吗?https://www.cnblogs.com/findumars/p/9285713.html

芯片春秋: 开源架构RISC-V前世今生 https://blog.csdn.net/BtB5e6Nsu1g511Eg5XEg/article/details/80267054

基于RISC-V架构的开源处理器及SoC研究综述(一) https://blog.csdn.net/leishangwen/article/details/55006662

如何看待开源指令集RISC-V https://www.zhihu.com/question/28368960

SiFive引发了一场开源芯片设计革命 http://www.elecfans.com/emb/dsp/20180518679533.html

华米发布黄山1号 https://www.expreview.com/64167.html

华米发布黄山1号 https://www.techsir.com/a/201809/49150.html

中国开放指令生态(RISC-V)联盟成立 https://www.xianjichina.com/special/detail_367735.html

出货量8亿颗!阿里系芯片公司中天微发布中国自研CPU架构RISC-V处理器 http://www.sohu.com/a/251828505_473283

从落地产品看RISC-V中国芯势力 http://dy.163.com/v2/article/detail/ED2IBJU50511RIVP.html

全球首款基于 RISC-V 的开源硬件板卡 — HiFive https://www.oschina.net/news/93390/hifive-unleashed