【栏目介绍:"玩转OurBMC"是OurBMC社区开创的知识分享类栏目,主要聚焦于社区和BMC全栈技术相关基础知识的分享,全方位涵盖了从理论原理到实践操作的知识传递。OurBMC社区将通过"玩转OurBMC"栏目,帮助开发者们深入了解到社区文化、理念及特色,增进开发者对BMC全栈技术的理解。

欢迎各位关注"玩转OurBMC"栏目,共同探索OurBMC社区的精彩世界。同时,我们诚挚地邀请各位开发者向"玩转OurBMC"栏目投稿,共同学习进步,将栏目打造成为汇聚智慧、激发创意的知识园地。】

随着异构计算(CPU、GPU、FPGA、AI加速器)的普及,传统互连协议(如PCIe)在缓存一致性、内存共享和低延迟通信方面的局限性逐渐暴露。CXL(Compute Express Link)应运而生,其目标是构建一个统一的缓存一致性协议,支持CPU与加速器、内存扩展设备之间的高效协作。本文旨在为读者普及CXL协议的基础知识,助力其深入理解并有效运行这一技术。

CXL 概述

CXL 最初由 Intel 公司于 2019 年首次公开讨论,后来得到了AMD、谷歌和微软等公司的支持。该技术旨在解决 CPU 与加速器、内存之间的数据传输瓶颈。其技术基础源自 PCIe(Peripheral Component Interconnect Express),但通过增强缓存一致性和内存共享功能,其性能得到显著提升。其历史与发展简介如下:

- 2019年:CXL 1.0/1.1版本发布,基于PCIe 5.0,引入缓存一致性协议(CXL.cache)和内存扩展协议(CXL.mem)。

- 2020年:CXL 2.0发布,支持内存池化和交换机架构,实现多主机共享内存资源。

- 2022-2024年:CXL 3.0/3.1/3.2版本发布,基于PCIe 6.0物理层,带宽提升至64 GT/s,新增分布式计算支持、增强内存池功能,并优化安全性。

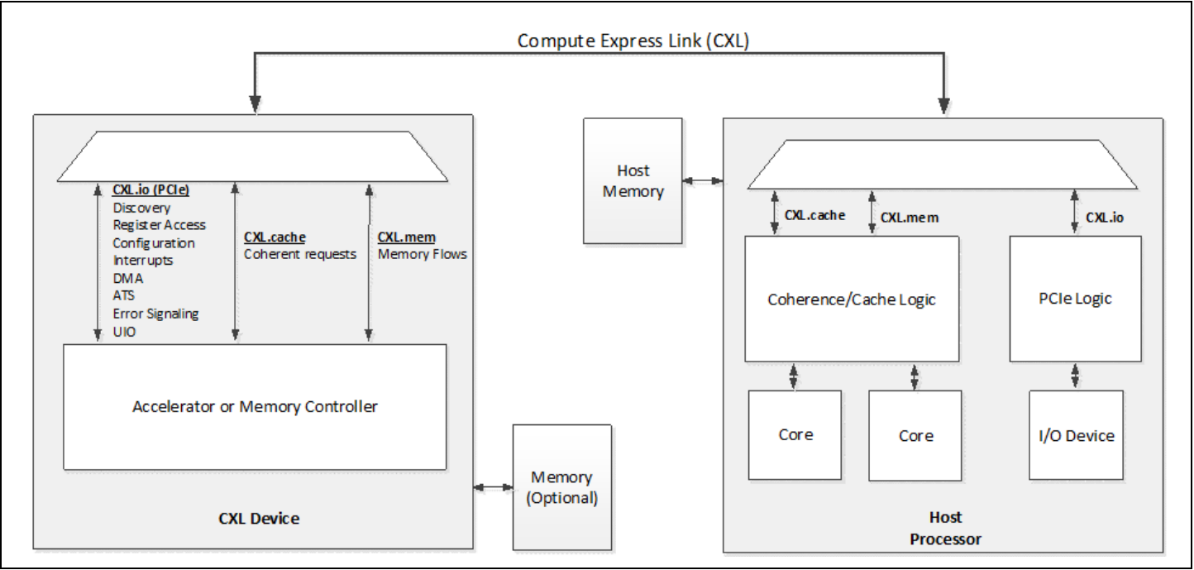

![a19ae0018bdafb48f343396cf53513ae.png]()

注:上图引用< Compute Express Link Specification Revision 3.1, Version 1.0>

图1 处理器与CXL设备连接概念图

01 CXL的主要功能

(1)缓存一致性:CXL 通过一致性协议(CXL.cache)确保多设备共享内存时数据同步,减少冗余数据传输。

(2)内存池化与共享:支持动态分配内存资源,允许多主机共享内存池,提升资源利用率。

(3)低延迟与高带宽:通过简化协议栈(如减少数据包开销)和优化物理层(如PCIe 6.0),实现纳秒级延迟与 64 GT/s带宽。

(4)异构计算支持:无缝连接 CPU、GPU、FPGA 和存储设备,促进协同计算。

02 CXL的应用场景(包括但不限于以下内容)

(1)高性能计算:加速大规模模拟与建模任务,如气象预测和流体力学计算。

(2)人工智能与机器学习:优化 GPU 与 CPU 之间的数据交换效率,缩短模型训练时间。

(3)数据中心:实现内存池化与动态扩展,支持多租户环境下的资源隔离与共享。

(4)存储与内存扩展:通过 CXL.memory 协议扩展服务器内存容量,支持非易失性内存(NVM)应用。

(5)边缘计算与云计算:在分布式架构中实现低延迟资源共享,提升边缘节点的计算能力。

03 CXL实际应用中的优势与局限性

优势: (1)性能提升:相比 PCIe,带宽提升 2 倍以上且延迟降低。

(2)兼容性:基于 PCIe 物理层,兼容现有硬件基础设施。

(3)灵活性:支持多种设备类型和拓扑结构(如直连、交换集群)。

(4)生态扩展:目前已有 200 多家企业加入 CXL 联盟,三星、美光等厂商推出了商用产品。

局限性:

(1)技术复杂性:需高度优化的硬件设计,增加系统开发成本。

(2)兼容性限制:旧设备需额外转换器才能支持 CXL 协议。

(3)安全风险:共享内存可能引发数据泄露,需依赖加密与隔离机制。

(4)初期成本高:CXL 设备价格高于传统 PCIe 设备,需要一定时间普及。

CXL 协议作为一种创新的接口标准,在高性能计算、人工智能、数据中心等领域具有广泛的应用前景。随着技术的不断进步和成本的逐渐降低,CXL 协议有望在未来得到更广泛的推广和应用。下面对 CXL 协议相关内容进行详解。

CXL 协议介绍

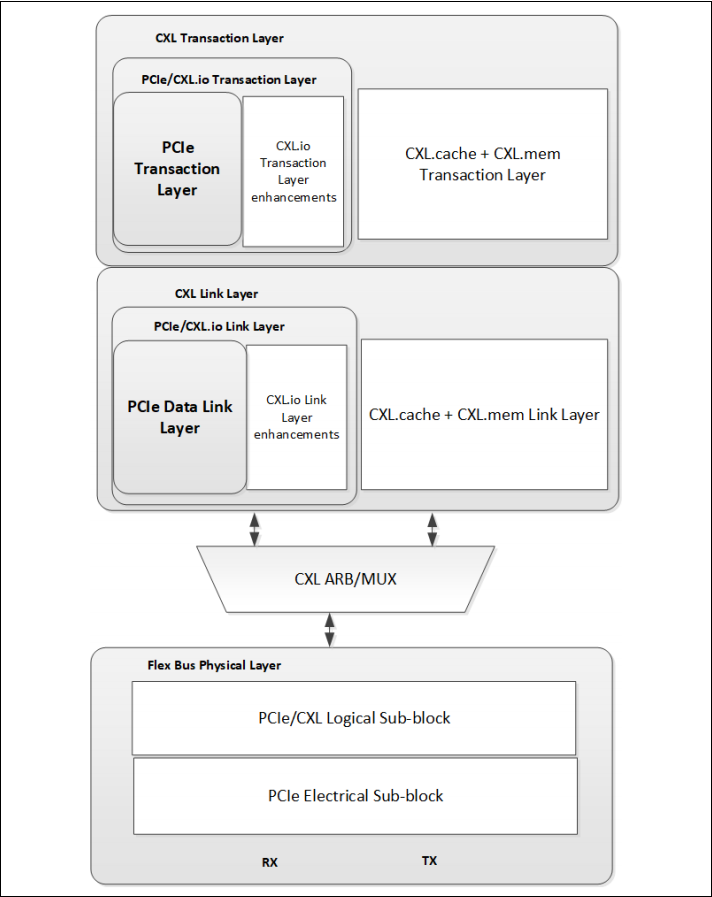

![fa001e8c2e7bcd414dbaa81ed2e3bb24.png]()

注:上图引用< Compute Express Link Specification Revision 3.1, Version 1.0>

图2 CXL Flex Bus分层概念图

Flex Bus 是 CXL 中定义的一种技术,它允许主机系统中的插槽既可以作为 PCIe插槽使用,也可以作为 CXL 插槽使用,这种灵活性称为 Flex Bus,它在链路训练过程中能够协商决定使用 PCIe 模式还是 CXL 模式。

Flex Bus 架构被组织为多个层,如上图2 所示。CXL 事务(协议)层细分为处理 CXL.io 的逻辑和处理 CXL.cache 和 CXL.mem 的逻辑;CXL 链路层以相同方式细分。同时 CXL.cache 和 CXL.mem 逻辑在事务层和链路层内组合。CXL 链路层与物理层之间有一个 CXL 仲裁和多路复用(ARB/MUX)接口,用于交错来自两个逻辑流的流量。

CXL 协议基于 PCIe 5.0/6.0 物理层构建,在逻辑上分为三个独立协议层(Protocol Layer),分别对应不同的功能。其中,CXL.io 兼容 PCIe 的 I/O 协议,负责设备发现、配置、中断、DMA 等传统操作。CXL.cache 实现设备与主机之间的缓存一致性,支持细粒度(缓存行级别)一致性管理。CXL.mem 允许主机或设备以低延迟直接访问对方的内存,支持原子操作和内存语义。以下是对各协议的详细阐述:

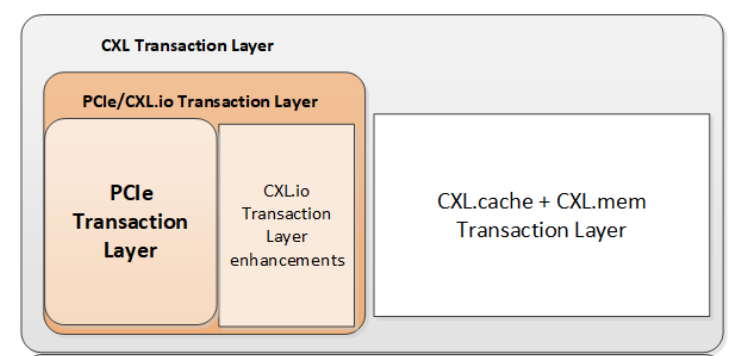

![19515725e12ec63cdacd4685588aac09.png]()

注:上图引用< Compute Express Link Specification Revision 3.1, Version 1.0>

图3 CXL Transaction Layer

CXL.io 是 CXL 协议的基石,直接继承并扩展了 PCIe 的 I/O 协议。它的核心功能包括:

(1)设备枚举与配置:发现 CXL 设备并分配资源(如内存地址空间、中断号)。

(2)传统 I/O 操作:支持 PCIe 的 Memory Read/Write、IO Read/Write、配置空间访问。

(3)中断传递:处理设备到主机的中断请求(MSI/MSI-X)。

(4)DMA 支持:允许设备通过 Bus Master 发起 DMA 操作(尽管 CXL.cache 和 CXL.mem 可以替代部分 DMA 场景)。

CXL.io 支持 PCIe 的所有事务类型,并新增了 CXL 专用事务(通过PCIe的 Vendor-Specific Message实现):

(1)内存读写(Memory Read/Write):用于访问设备的 MMIO(Memory-Mapped I/O)空间,例如控制寄存器。事务格式与 PCIe 相同,包含地址、数据长度(DW)、TLP 头部等。

(2)配置读写(Configuration Read/Write):用于访问 PCIe 配置空间(如BAR寄存器、设备ID、厂商ID)。还包括其它配置空间扩展:CXL 设备在 PCIe 配置空间中新增了 CXL Capability Structure,用于协商 CXL.cache 和 CXL.mem 的支持。

(3)消息事务(Message Transactions):包括中断请求(MSI/MSI-X)、错误报告(Error Signaling)、热插拔事件等。还包括 CXL 专用消息如 CXL.mem Protocol Negotiation Request,用于在链路初始化阶段协商支持的协议。

以 CXL Type1 设备为例,其 CXL.io 的配置流程并非一个独立的过程,而是与 CXL 设备的整体配置和初始化流程紧密结合的。以下是对该流程的一个概述:

(1)链路初始化(Link Training):物理层协商速率(如 PCIe 5.0的32 GT/s)以及通道宽度(x16/x8/x4)等。通过 PCIe 的 LTSSM(Link Training and Status State Machine)完成。

(2)设备发现与枚举:主机通过 PCIe 配置空间读取设备的 Vendor ID 和 Device ID,识别为 CXL 设备。主机检查设备的 CXL Capability Structure,确认其支持的协议(如 Type1 设备支持 CXL.io + CXL.cache)。

(3)资源分配:BAR(Base Address Register)设置:主机为设备的 MMIO 空间分配物理地址。例如:Type1 设备可能需要 1MB 的 MMIO 空间用于控制寄存器。同时为设备分配 MSI/MSI-X 中断资源。

(4)协议协商:主机通过 CXL.io 发送 CXL Protocol Negotiation Request,与设备协商 CXL.cache 的版本(如CXL2.0或3.0)和参数(如缓存行大小、一致性粒度)。

(5)设备就绪:设备进入运行状态,开始处 CXL.cache 请求或 CXL.mem 访问。

02 CXL.cache

CXL.cache 的主要作用如下:

(1)缓存主机内存中的数据:CXL.cache 允许设备(如GPU或FPGA)缓存主机内存中的数据,并支持缓存一致性。这意味着设备可以直接访问和操作主机内存中的数据,而无需通过 CPU 进行数据复制,从而提高数据访问效率。

(2)加速内存密集型工作负载:通过缓存一致性减少数据复制开销,CXL.cache有助于加速内存密集型工作负载。这使得设备能够更快速地访问和处理数据,提高整体系统性能。

(3)硬件实现缓存一致性协议:CXL.cache 通过硬件实现缓存一致性协议,确保设备和主机之间的缓存数据保持一致性。这有助于维护数据的一致性,避免因缓存不一致导致的错误。

(4)支持 CPU 和设备共享内存缓存:CXL.cache 支持 CPU 和设备(如GPU或FPGA)共享内存缓存,这有助于减少数据在 CPU 和设备之间的传输,提高数据处理效率。

(5)解决内存带宽和容量扩展挑战:CXL.cache 使连接到 CXL 设备的内存可映射到系统可缓存内存空间,有利于异构处理,并有助于应对内存带宽和容量扩展挑战。

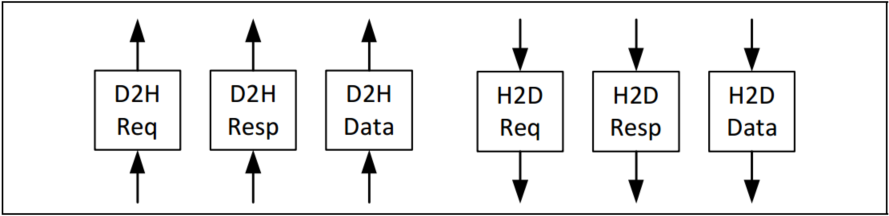

CXL.cache 协议将设备和主机之间的交互定义为多个请求,每个请求至少有一个相关的响应消息,有时还有数据传输。接口在每个方向上由三个通道组成:请求、响应和数据。这些通道根据其方向命名:

D2H------表示设备到主机;

H2D------表示主机到设备;

如下图4 所示,独立通道允许不同类型的消息使用专用线路,并实现解耦和每条线路更高的有效吞吐量。

![e874600fd023f46a91ddcf64f772efab.png]()

注:上图引用< Compute Express Link Specification Revision 3.1, Version 1.0>

图4 CXL.cache 通道

D2H 将新请求从设备传送到主机。这些请求通常以内存为目标。每个请求将收到零个、一个或两个响应,以及最多一个 64 字节的缓存行数据。D2H 响应将设备的所有响应传送到主机。H2D 请求携带主机到设备的请求,用于保持一致性的监听,监听时可能会返回数据。

CXL.cache 协议中,通道信用(Channel Crediting)是一种流控制机制,用于管理设备和主机之间消息的发送和接收。由于不能假设在通道上发送消息的能力始终可用,因为链路层信用可能并非始终可用,所以每个通道必须使用信用来发送任何消息,并从接收方收集信用回报。

在操作过程中,接收方在处理消息时返回一个信用,即释放一个缓冲区。不需要双方都记入所有信用,只要信用计数器饱和即可。发送方如果没有可用的信用,则必须等待接收方返回一个信用。

下方表格中描述了哪些通道必须耗尽才能保持向前进展,哪些通道可以无限期阻塞:

![f54fbc72e62086d3da612aac99b7f58c.png]()

注:上表引用< Compute Express Link Specification Revision 3.1, Version 1.0>

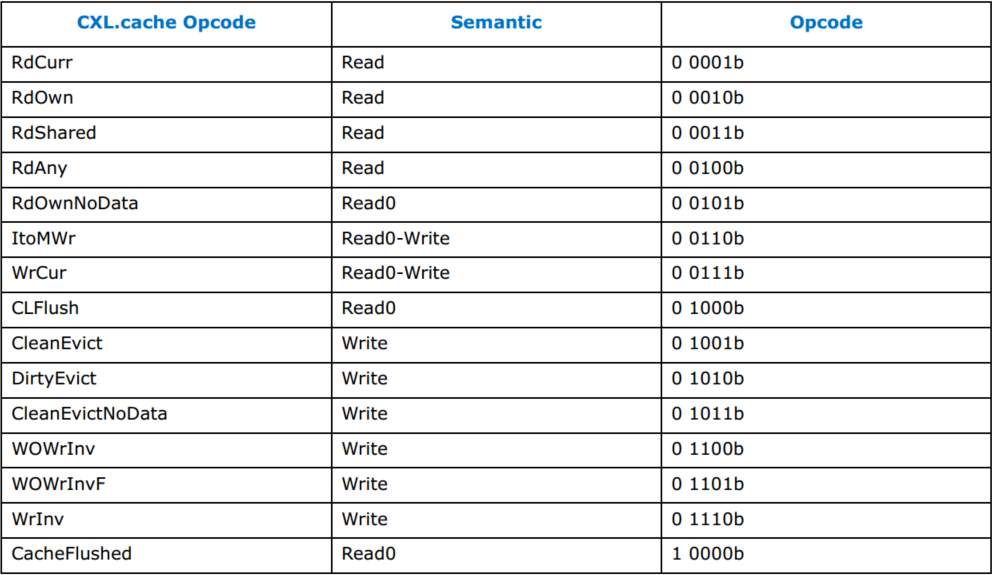

CXL.cache 协议中,设备(Device)向主机(Host)发起的一系列请求操作。下表操作码定义了设备如何与主机进行数据交互,以实现缓存一致性和数据传输:

![b7f0f607c5f79bda2ecff1e38d3b0443.png]()

注:上表引用< Compute Express Link Specification Revision 3.1, Version 1.0>

(1)RdCurr:来自设备的完整缓存行读取请求,用于获取最新数据,但不会更改任何缓存(包括主机)中的现有状态。

(2)RdOwn:设备发出的完整缓存行读取请求,用于以任何可写状态缓存行。

(3)RdShared:设备发出的、用于在共享状态下缓存行的完整缓存行读取请求。

(4)RdAny:设备发出的完整缓存行读取请求,用于在任何状态下缓存行。

(5)RdOwnNoData:用于获取地址字段中指示的缓存行地址的独占所有权。典型的响应是独占 (GO-E)。

(6)ItoMWr:此命令请求对地址字段中指示的缓存行地址的独占所有权,并以原子方式将缓存行写回主机。

(7)WrCur:该命令类似于 ItoMWr,它会以原子方式请求缓存行的所有权,然后将完整的缓存行写回 Fabric。

(8)CLFlush:向主机发出的请求,以使地址字段中指定的缓存行无效。

(9)CleanEvict:向主机发出的从设备中驱逐完整64字节独占缓存行的请求。

(10)DirtyEvict:向主机发出的从设备中驱逐完整64字节修改缓存行的请求。

(11)CleanEvictNoData:设备向主机更新设备中已删除干净线路的请求。

(12)WOWrInv:用于写入组合类型存储的0-63字节弱序写入无效行请求。可以设置任何字节启用组合。

(13)WOWrInvF:与WOWrInv相同,它是64字节的写入。

(14)WrInv:这是0-64字节的写入无效行请求。通常WrInv会收到WritePull,然后收到GO。

(15)CacheFlushed:设备发送的指示,用于通知主机其缓存已刷新,并且不再包含处于共享、独占或修改状态的任何缓存行。

03 CXL.mem

CXL.mem 主要作用如下:

(1)多种内存连接选项:CXL.mem 支持多种不同的内存连接选项,包括内存控制器位于主机 CPU 中、加速器设备中,或内存控制器移至内存冲芯片时的情况。

(2)支持不同类型的内存:CXL.mem 适用于不同类型的内存,例如易失性、持久性等,以及不同的配置,如扁平结构、层次结构等。

(3)提供一致性模型:CXL.mem 为主机管理的设备内存(HDM)地址区域提供了三种基本的一致性模型,包括仅主机一致性(HDM-H)、设备一致性(HDM-D)和 HDM-DB。

(4)直接加载/存储访问:CXL.mem 允许直接加载/存储访问共享内存,这意味着设备可以直接访问和操作主机内存中的数据,无需通过 CPU 进行数据复制,从而提高数据访问效率。

(5)对等通信:CXL 允许使用 CXL.mem 协议进行对等通信,这意味着设备之间可以直接交换数据,进一步提高数据处理的效率。

CXL.mem 协议定义了三种基本一致性模型,以适应不同类型的设备需求:

(1)HDM-H(仅主机一致性):仅用于Type3设备。

(2)HDM-D(设备一致性):仅用于依赖CXL.cache管理与主机一致性的传统Type2型设备。

(3)HDM-DB(使用Back-Invalidate的设备一致性):可供Type2设备或Type3设备使用。

CXL.mem协议还提供了两种主要事务类型,以支持设备与主机之间的内存访问:

(1)Host-to-Device访问:主机通过CXL.mem读写设备的本地内存(如GPU显存)。

(2)Device-to-Host访问:设备通过CXL.mem读写主机内存(替代部分DMA场景)。

在地址转换与虚拟化方面,CXL.mem 协议实现了以下功能:

(1)主机访问设备内存:主机会将设备内存映射到自身的物理地址空间(通过 Host Physical Address, HPA),过程如下:

a、设备在初始化时上报内存容量和地址范围。

b、主机的内存控制器将设备内存映射到HP的特定区域(例如0x100000000-0x1FFFFFFFF)。

c、操作系统通过 ACPI 表(如SRAT/SLIT)识别设备内存为 NUMA 节点。

(2)设备访问主机内存:设备使用设备物理地址(DPA),需通过地址转换或 IOMMU 转换为 HPA。

以 Type3 设备(内存扩展)为例,CXL.mem 的配置与管理流程如下:

(1)设备初始化:设备通过 CXL.io 的 PCI 配置空间或 ACPI 表上报内存容量,主机在启动时通过 ACPI 的 CEDT(CXL Early Discovery Table)识别设备。

(2)地址分配:主机内存控制器将设备内存映射到 HPA 的空闲区域(例如从 0x8000000000 开始)。

(3)操作系统集成:Linux内核通过 CXL 驱动将设备内存注册为 NUMA 节点(如 numa_node=1)。应用通过 numactl 命令或 API 显式分配设备内存。

此外,CXL.mem 协议还支持内存交错(Interleaving)机制,允许将设备内存划分为多个通道进行并行读写,从而提升带宽和性能。

本期内容深入解析了 CXL 协议的核心概念、协议架构及其具体内容,全方位展现了 CXL 协议的基础与精髓。下期我们将进一步拓展探讨 CXL 协议的维度,聚焦于 CXL 设备的多样化类型以及 CXL 设备在固件端的支持情况,您将了解到 CXL 协议如何适应并优化不同类型的设备,以及设备固件在 CXL 协议实现中所扮演的关键角色。欢迎大家关注!